# ATJ2091H PRODUCT DATA SHEET

# **Declaration**

Circuit diagrams and other information relating to products of Actions Semiconductor Company, Ltd. ("Actions") are included as a means or illustrating typical applications. Consequently, complete information sufficient for construction purposes is not necessarily given. Although the information has been examined and is believed to be accurate, Actions makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and disclaims any responsibility for inaccuracies. Information in this document is provided solely to enable use of Actions' products. The information presented in this document does not form part of any quotation or contract for sale. Actions assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Actions' products, except as may expressly be provided in Actions' Terms and Conditions of Sale for such products. All sales of any Actions products are expressly conditional on your agreement to the terms and conditions of the most recently dated version of Actions' Terms and Conditions of Sale Agreement dated before the date of your order.

The provision of this information does not convey to the purchaser of the described semiconductor devices any licenses under any patent rights, copyright, trademark rights, rights in trade secrets and/or know how, or any other intellectual property rights of Actions or others, however denominated, whether by express or implied representation, by estoppel, or otherwise.

Information contained herein relates solely to the Actions products described herein and abrogates and supersedes, as of the release date of this publication, all previously published data and specifications relating to such products provided by Actions or by any other person purporting to distribute such information. Actions reserves the right to make changes to specifications and product descriptions at any time without notice. Contact your Actions sales representative to obtain the latest specifications before placing your product order. Actions product may contain design defects or errors known as anomalies or errata which may cause the products functions to deviate from published specifications. Anomaly or "errata" sheets relating to currently characterized anomalies or errata are available upon request. Designers must not rely on the absence or characteristics of any features or instructions of Actions' products marked "reserved" or "undefined." Actions reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Actions' products are not designed, intended, authorized or warranted for use in any life support or other application where product failure could cause or contribute to personal injury or severe property damage. Any and all such uses without prior written approval of an Officer of Actions and further testing and/or modification will be fully at the risk of the customer.

Copies of this document and/or other Actions product literature, as well as the Terms and Conditions of Sale Agreement, may be obtained by visiting Actions' website at http://actions.com.cn or from an authorized Actions representative. The word "ACTIONS," the Actions' LOGO, whether used separately and/or in combination, and the phase "ATJ2091H" are trademarks of Actions Semiconductor Company, Ltd.. Names and brands of other companies and their products that may from time to time descriptively appear in this

product data sheet are the trademarks of their respective holders: no affiliation, authorization, or endorsement by such persons is claimed or implied except as may be expressly stated therein.

ACTIONS DISCLAIMS AND EXCLUDES ANY AND ALL WARRANTIES, INCLUDING WITHOUT LIMITATION ANY AND ALL IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE, AND AGAINST INFRINGEMENT AND THE LIKE, AND ANY AND ALL WARRANTIES ARISING FROM ANY COURSE OF DEALING OR USAGE OF TRADE.

IN NO EVENT SHALL ACTIONS BE RELIABLE FOR ANY DIRECT, INCIDENTAL, INDIRECT, SPECIAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES; OR FOR LOST DATA, PROFITS, SAVINGS OR REVENUES OF ANY KIND; REGARDLESS OF THE FORM OF ACTION, WHETHER BASED ON CONTRACT; TORT; NEGLIGENCE OF ACTIONS OR OTHERS; STRICT LIABILITY; BREACH OF WARRANTY; OR OTHERWISE; WHETHER OR NOT ANY REMEDY OF BUYER IS HELD TO HAVE FAILED OF ITS ESSENTIAL PURPOSE, AND WHETHER ACTIONS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES OR NOT.

### **ADDITIONAL SUPPORT**

Additional product and company information can be obtained by going to the Actions website at: <a href="https://www.actions-semi.com">www.actions-semi.com</a>

# **Table of Contents**

| ATJ2091H PRODUCT DATA SHEET     | 1  |

|---------------------------------|----|

| Declaration                     | 1  |

| ADDITIONAL SUPPORT              | 2  |

| 1. Introduction                 | 5  |

| 2. Features                     | 5  |

| ATJ2091H Features:              | 5  |

| 3. Pin Description              |    |

| 3.1 Pin Out                     | 7  |

| Function Description            | 11 |

| 4.1 Functional Block Diagram    |    |

| 4.2 MCU Core                    |    |

| 4.2.1 MCU Memory                |    |

| 4.2.2 MCU 64kb Memory Space     |    |

| 4.4 DMA Controller              |    |

| 4.5 General Purpose IO Ports    |    |

| 4.6 RTC/CTC/Watch Dog Timer     |    |

| 4.6.1 RTC                       |    |

| 4.6.2 CTC                       |    |

| 4.6.3 Watchdog                  | 14 |

| 4.7 Power Management Unit (PMU) | 14 |

| 4.7.1 Power Supply Modes        | 14 |

| 4.8 LCD Interface               |    |

| 4.9 Key Scan Interface          |    |

| 4.10 External Memory Interface  |    |

| 4.10.1 NAND Flash Interface     |    |

| 4.11 USB 2.0 SIE                |    |

| 4.11.1General Description       |    |

# ATJ2091H PRODUCT DATASHEET

| 4.11.2 Features                                 | 17 |

|-------------------------------------------------|----|

| 4.11.3 Flash Interface                          | 17 |

| 4.11.4 USB Using Memory                         | 18 |

| 5. Electrical Characteristics                   | 19 |

| 5.1 Absolute Maximum Ratings                    | 19 |

| 5.2 Capacitance                                 | 19 |

| 5.3 DC Characteristics                          | 20 |

| 5.4 AC Characteristics                          | 21 |

| 5.4.1 AC Test Input Waveform                    | 21 |

| 5.4.2 AC Test Output Measuring Points           | 21 |

| 5.4.3 Reset Parameter                           | 21 |

| 5.4.4 Initialization Parameter                  | 21 |

| 5.4.5 GPIO Interface Parameter                  | 22 |

| 5.4.6 Ordinary ROM Parameter                    | 23 |

| 5.4.7 External System Bus Parameter             | 23 |

| 5.4.8 Bus Operation                             | 24 |

| 5.4.9 A/D Converter Characteristics             | 25 |

| 5.4.10 Headphone Driver Characteristics Table   | 25 |

| 5.4.11 LCM Driver Parameter                     | 27 |

| 6. Ordering Information                         | 28 |

| 6.1 Soldering Conditions                        | 28 |

| 6.2 Precaution Against ESD For Semiconductors   |    |

| 6.3 Handling of Unused Input Pins For CMOS      |    |

| 6.4 Status Before Initialization of MOS Devices |    |

| 7. ATJ 2091H Package Drawing                    | 30 |

# 1. Introduction

ATJ2091H is a new generation single-chip highly-integrated digital multimedia SOC for devices such as dedicated audio players, photo viewers, PDAs. It includes audio codec, image and video decoding engine, a high performance 2 core (DSP and MCU) structure with embedded RAM and ROM, digital record capabilities and USB interface for downloading and uploading. ATJ2091H also provides an interface to flash memory, LED/LCD/OLED, button and switch inputs, headphones, microphone while ATJ2091H also can interface to FM input and control. ATJ2091H contains a high performance DSP, which can easily be programmed to support many kinds of digital audio standards such as MP3, WMA, etc. As storage devices ATJ2091H can act as a USB mass storage slave device to personal computer system. ATJ2091H has low power consumption to allow long battery life and an efficient flexible on-chip voltage converter that allows many different battery configurations, including 1xAA, 1xAAA, 2xAA, 2xAAA and Li-Lon. The built-in Sigma-Delta DAC includes a headphone driver to directly drive low impedance headphones. The ADC includes inputs for both Microphone and Analog Audio in to support voice recording. ATJ2091H also has radio integration features. ATJ2091H provides a true 'ALL-IN-ONE' solution that is ideally suited for highly optimized digital multimedia players.

# 2. Features

### ATJ2091H Features:

- Digital voice recording at ultra low 8Kbps with Actions speech algorithm

- 24 bits DSP core with on-chip debug support unit (DSU)

- 8 bits MCU which instruction set is compatible with Z80

- Support up to 3 (pcs)\* 64M ~4G bytes NAND type/SLC/MLC flash

- Support 24MHz OSC with on-chip PLL for DSP

- 2-channel DMA, 1-channel CTC (Counter/Timer Controller) and interrupt controller for MCU

- Energy saving power management (PMU), supporting 1xAA, 1xAAA, 2xAA,2xAAA and Li-Lon

- USB 2.0 high speed, act as mass storage device

- Build in Stereo Sigma-Delta DAC and its modulator digital out

# ATJ2091H PRODUCT DATASHEET

- Support external 80 series LCM driver interface

- Support stereo Sigma-Delta ADC for microphone/ line Input, sample rate at 8/12/16/22/24/32/48KHz

- Support digital audio encoding with sample rate of 8-48KHz

- DSP+PM/DM speed up to 72MIPS

- Headphone driver output 2x11Mw @16ohm

- Package at LQFP-64 (10x10mm)

- FM tuner mixer and controller

- Supports stereo sigma-Delta ADC for FM input, sample rate at 8/12/16/22/24/32/48KHz

# 3. Pin Description

### NOTE:

1: PWR---Power Supply 2: Al---Analog Input 3: AO---Analog Output 4: O---Output 5: I---Input 6: BI---Bi-direction 7: USCU,USCL--- Schmitt Type 8: OD—Open Drain

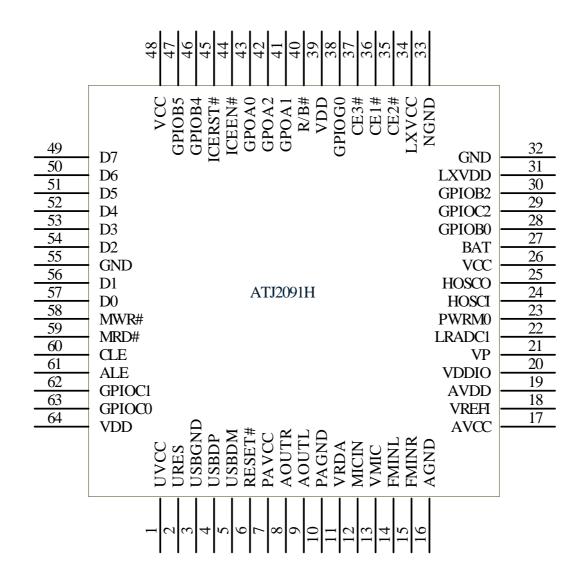

### 3.1 Pin Out

# 3.1.1 Pin Sort by Pin Number

### ATJ2091H

| Pin No. | Pin           | I/O Type | Driver | Reset   | Short Description                     |

|---------|---------------|----------|--------|---------|---------------------------------------|

|         | Name          |          |        | Default | -                                     |

| 1       | UVCC          | PWR      | /      | /       | Power supply for USB                  |

| 2       | URES          | AO       | /      | /       | USB precision Resistor                |

| 3       | USBGND        | PWR      | /      | /       | USB ground                            |

| 4       | USBDP         | Α        | /      | Н       | USB data minus                        |

| 5       | USBDM         | А        | /      | Н       | USB data plus                         |

| 6       | RESET-        | I        | /      | Н       | System reset input (active low)       |

| 7       | PAVCC         | PWR      | /      | /       | Power supply for power amplifier      |

| 8       | AOUTR         | AO       | /      | /       | Int. PA right channel analog output   |

| 9       | AOUTL         | AO       | /      | /       | Int. PA left channel analog output    |

| 10      | PAGND         | PWR      | /      | /       | Power amplifier ground                |

|         | \(\text{DD}\) |          | ,      |         | Bypass capacitor connect pin for Int. |

| 11      | VRDA          | AO       | /      | /       | D/A Reference voltage                 |

| 12      | MICIN         | Al       | /      | /       | Microphone pre-amplifier input        |

| 13      | VMIC          | PWR      | /      | /       | Power supply for Microphone           |

| 14      | FMINL         | Al       | /      | /       | Left channel of FM line input         |

| 15      | FMINR         | Al       | /      | /       | Right channel of FM line input        |

| 16      | AGND          | PWR      | /      | /       | Analog ground                         |

| 17      | AVCC          | PWR      | /      | /       | power supply of Analog                |

| 18      | VREFI         | Al       | /      | /       | Voltage reference input               |

| 19      | AVDD          | PWR      | /      | /       | Analog Core power pin                 |

| 20      | VDDIO         | PWR      | /      | /       | Core power input/output               |

| 21      | VP            | PWR      | /      | /       | Power pin                             |

| 22      | LRADC1        | Al       | /      | /       | Low resolution A/D input 1            |

| 23      | PWRM 0        | Al       | /      | /       | POWER mode select 0                   |

| 24      | HOSCI         | Al       | /      | /       | High frequency crystal OSC input      |

# ATJ2091H PRODUCT DATASHEET

| 25 | HOSCO   | AO  | /      | /  | High frequency crystal OSC output        |

|----|---------|-----|--------|----|------------------------------------------|

| 26 | VCC     | PWR | /      | /  | PAD power pin                            |

| 27 | BAT     | I   | /      | /  | Battery monitor pin.                     |

|    | GPIO_B0 | BI  |        | Z  | Bit0 of General purpose I/O port B       |

| 28 | KEYI0   | I   | 2mA    | Н  | Bit0 of key scan circuit input           |

| 29 | GPIO_C2 | BI  | 4mA    | 1  | Bit2 of General purpose I/O port C       |

| 00 | GPIO_B2 | ВІ  | 404    | Z  | Bit2 of General purpose I/O port B       |

| 30 | KEYI2   | Ι   | 10mA   | Н  | Bit2 of key scan circuit input           |

| 31 | LXVDD   | PWR | /      | 1  | Connect to VDD inductance                |

| 32 | GND     | PWR | /      | 1  | Ground                                   |

| 33 | NGND    | PWR | /      | 1  | NMOS Ground                              |

| 34 | LXVCC   | PWR | /      | 1  | Connect to VCC inductance                |

| 35 | CE2-    | 0   | /      | Н  | Ext. memory chip enable 2                |

| 36 | CE1-    | 0   | /      | Н  | Ext. memory chip enable 1                |

| 07 | CE3-    | 0   | 4 A    | Н  | Ext. memory chip enable 3                |

| 37 | GPO_A3  | 0   | 4mA    | 1  | Bit3 of General purpose port A           |

| 38 | GPIO_G0 | ВІ  | 2mA    | Z  | Bit0 of General purpose I/O port G       |

| 39 | VDD     | PWR | /      | 1  | Digital Core power                       |

| 40 | RB-     | I   | /      | OD | Nand Type flash Ready/Busy status input. |

| 44 | GPO_A1  | 0   | 4 ma A | L  | Bit1 of General purpose Output port A    |

| 41 | ICECK   | I   | 4mA    | 1  | Clock input of DSU                       |

| 42 | GPO_A2  | 0   | 4mA    | L  | Bit2 of General purpose Output port A    |

| 42 | ICEDO   | 0   | 4IIIA  | 1  | Data output of DSU                       |

| 43 | GPO_A0  | 0   | 4mA    | 0  | Bit0 of General purpose Output port A    |

| 43 | ICED1   | I   | 4IIIA  | /  | Data input of DSU                        |

| 44 | ICEEN-  | I   | /      | 1  | DSU enable (active low)                  |

| 45 | ICERST- | I   | /      | 1  | DSU reset (active low)                   |

| 46 | GPIO_B4 | ВІ  | 10mA   | Z  | Bit4 of General purpose I/O port B       |

| 46 | KEYO0   | 0   | TOMA   | /  | Bit0 of key scan circuit output          |

| 47 | GPIO_B5 | ВІ  | 10mA   | Z  | Bit5 of General purpose I/O port B       |

# ATJ2091H PRODUCT DATASHEET

|    | KEYO1   | 0   |     | /  | Bit1 of key scan circuit output     |

|----|---------|-----|-----|----|-------------------------------------|

| 48 | VCC     | PWR | /   | ,  | Digital power pad                   |

| 49 | D7      | BI  | /   | L  | Bit7 of ext. memory data bus        |

|    |         |     | ,   |    | ·                                   |

| 50 | D6      | BI  | /   | L  | Bit6 of ext. memory data bus        |

| 51 | D5      | BI  | /   | L  | Bit5 of ext. memory data bus        |

| 52 | D4      | ВІ  | /   | L  | Bit4 of ext. memory data bus        |

| 53 | D3      | ВІ  | /   | L  | Bit3 of ext. memory data bus        |

| 54 | D2      | ВІ  | /   | L  | Bit2 of ext. memory data bus        |

| 55 | GND     | /   | /   | L  | GND                                 |

| 56 | D1      | ВІ  | /   | L  | Bit1 of ext. memory data bus        |

| 57 | D0      | BI  | /   | L  | Bit0 of ext. memory data bus        |

| 58 | MWR-    | 0   | /   | Н  | Ext. memory write strobe            |

| 59 | MRD-    | 0   | /   | Н  | Ext. memory read strobe             |

| 60 | CLE     | 0   | /   | L  | Command latch enable for NAND flash |

| 61 | ALE     | 0   | /   | L  | Address latch enable for NAND flash |

|    | GPIO_C1 | ВІ  |     | OD | Bit1 of General purpose I/O port C  |

| 62 | _SDA    | 0   | 2mA | /  | Serial data (Open drain)            |

|    | SIRQ-   | 1   |     | 1  | Ext. interrupt request input        |

| 63 | GPIO_C0 | BI  | 2mA | OD | Bit0 of General purpose I/O port C  |

| 64 | VDD     | PWR | /   | 1  | Digital Core power                  |

# Function Description

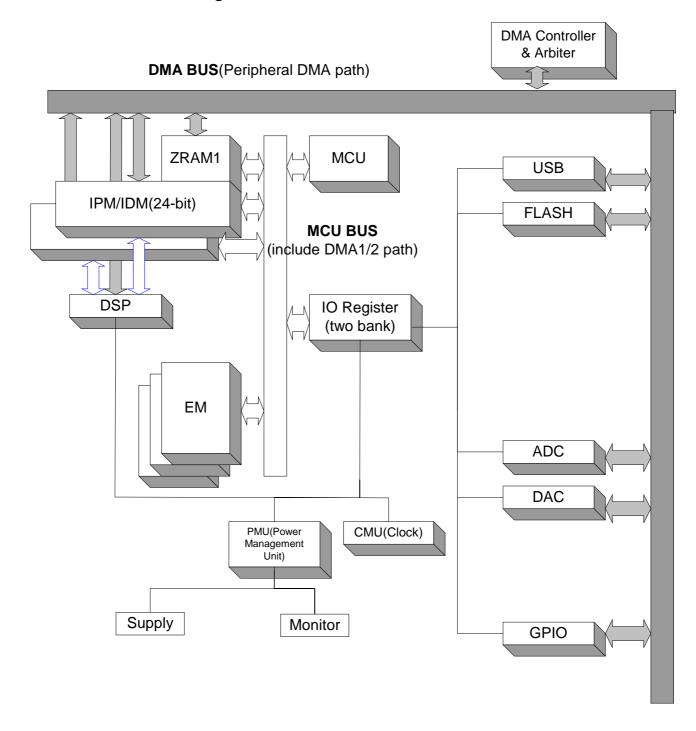

# 4.1 Functional Block Diagram

### 4.2 MCU Core

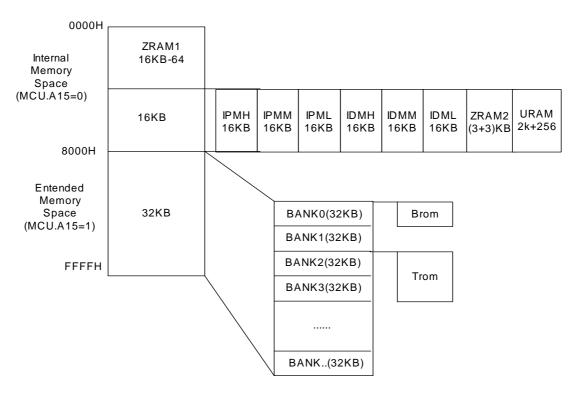

### 4.2.1 MCU Memory

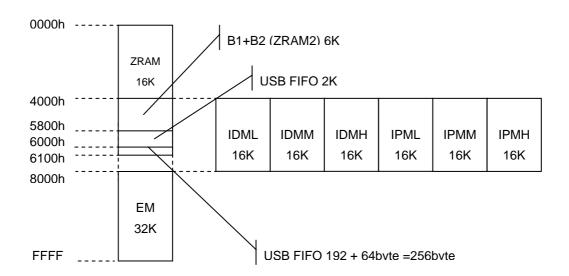

ATJ2091H includes120K+192=(16+6+2+16\*3+16\*3)K+256-64 bytes of on-chip SRAM and 50K=(12+21+17)k bytes on-chip ROM. See the following flag for on chip memory mapping.

- > (16K-64) byte ZRAM1(IA15=0,IA14=0): 0000H-3FBFH

- ➤ 6Kbyte ZRAM2 (IA15=0, IA14=1, IOReg05.[2:0]=111): 4000H-57FFH

- > ZRAM2 is make up of B1 and B2, each one is 3k\*8 byte SRAM. B1, B2 and ZRAM1(B0) can be operated severally.

### 4.2.2 MCU 64kb Memory Space

MCU 64KB Memory Space

### 4.3 DSP Core

24-bit Harvard architecture DSP with DSU built in. It works with a memory word length of 24 bits. ATJ2091H has 16KB\*24bit program memory (PM) and (16KB)\*24bit data memory (DM). Memory-Mapped register includes DAC interface.

### 4.4 DMA Controller

ATJ2091H supports 4 kinds of DMA channels. DMA1/2 support Data exchange in Memory or IO; DMA5 is for flash controller, DMA6 is USB DMA.

## 4.5 General Purpose IO Ports

ATJ2091H has GPOA, GPIOB, GPIOC, GPIOD, GPIOE, GPIOF, GPIOG and GPIOK. They have different functions in different modes.

| Func  | tion | <b>E</b> 4                                                                          | Ea                           | F3                            | E4          | <u> </u>        | Ee                | <b>E</b> 7      | F8        |  |

|-------|------|-------------------------------------------------------------------------------------|------------------------------|-------------------------------|-------------|-----------------|-------------------|-----------------|-----------|--|

| GPIO  | F1   |                                                                                     | F2                           | гэ                            | F4          | F5              | F6                | F7              | Γŏ        |  |

|       | 0    |                                                                                     |                              | 000 470 015                   | · 10        |                 |                   | N 04            | 000 4     |  |

| GPOA  | 1    |                                                                                     |                              | GPO_A [2~0] F                 | ins are IC  | EDO, ICECK      | and ICEL          | DI; Otherwise   | GPO_A     |  |

|       | 2    | [2~0] is us                                                                         | is used for output function. |                               |             |                 |                   |                 |           |  |

|       | 0    | At function                                                                         | n 1 (F1                      | l): When choo                 | sing keyb   | oard function   | , GPIOB           | [3~0] Pins ar   | e KEYI    |  |

|       | 1    | [3~0], and                                                                          | GPIOB                        | [7~4] are KE                  | /O [3~0];   | when not ch     | noosing k         | eyboard funct   | ion, as   |  |

|       | 2    | GPIOB [7                                                                            | ~0]; whe                     | en keyboard fu                | nction en   | ables, while    | some KE           | YI[30] is u     | sed as    |  |

|       | 3    | GPIOB, th                                                                           | e relativ                    | e keyin should                | be mask     | ed.GPIOB2/B     | 4/B5 hav          | e special larg  | e drive   |  |

| GPIOB | 4    | capability (                                                                        | up to 10r                    | nA,it can be use              | ed to drive | diode.          |                   |                 |           |  |

| GPIOB | 5    | At Function                                                                         | on2-8                        | ( <b>F2-F8</b> ): When        | n choosin   | g keyboard fu   | unction, G        | PIOB [3~0] F    | ins are   |  |

|       | 6    | KEYI [3~0], and GPIOB [7~4] are KEYO [3~0]; when not choosing keyboard function, as |                              |                               |             |                 |                   |                 |           |  |

|       |      | GPIOB [7                                                                            | ~0]; whe                     | en keyboard fu                | nction ena  | ables, while    | some KE           | YI [30] is u    | sed as    |  |

|       | 7    | GPIOB, th                                                                           | e relativ                    | e keyin should l              | oe maske    | d. Especially,  | when SP           | I function is e | nabled,   |  |

|       |      | GPIOB2 is                                                                           | used as                      | SPI_SCK and                   | GPIOB5 i    | s used as SP    | I_MOSI.           |                 |           |  |

|       |      | GPIOC0                                                                              | (F2-F8)                      | : When I <sup>2</sup> C fur   | nction ena  | bles, it is use | ed as _SC         | CL. When as     | IO, it is |  |

|       | 0    | GPIOCU                                                                              | GPIO_                        | C0, and then I <sup>2</sup> 0 | C can not   | be enabled si   | multaneou         | usly.           |           |  |

|       |      |                                                                                     | (F2-F8)                      | : When I <sup>2</sup> C fu    | nction en   | ables, it is u  | sed as _          | SDA. When e     | external  |  |

| GPIOC | 1    | GPIOC1                                                                              | interrup                     | ot enables, it is             | s SIRQ-;    | and when a      | s IO, it          | is GPIO_C; ı    | multiple  |  |

|       |      |                                                                                     | function                     | ns can not be er              | nabled sim  | nultaneously.   |                   |                 |           |  |

|       | 2    | GPIOC2/                                                                             | (F2-F8)                      | : GPIO_C2                     |             |                 |                   |                 |           |  |

|       | 3    | (F1-F                                                                               | <b>3):</b> GPIC              | C3 only                       |             | (F4             | - <b>F8)</b> : CE | 0_              |           |  |

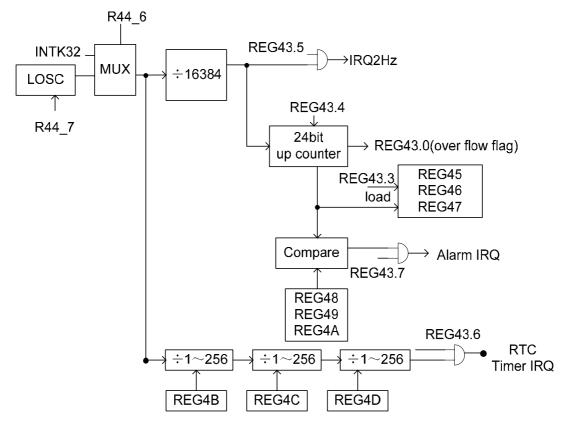

# 4.6 RTC/CTC/Watch Dog Timer

### 4.6.1 RTC

RTC is a 24-bits counter with the following function, the clock source is LOSC (95H only) or INTK32

- Time

- Alarm

- Timer

### 4.6.2 CTC

CTC is a counter whose clock source is different with RTC. The clock source is HOSC.

### 4.6.3 Watchdog

Watchdog can be set from 176-milisecond to 180-second with different step.

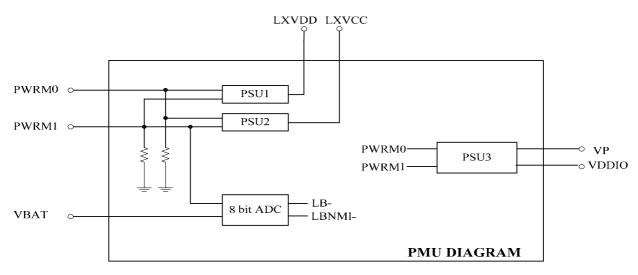

## 4.7 Power Management Unit (PMU)

### 4.7.1 Power Supply Modes

ATJ2091H can support 1xAA/AAA, 2xAA/AAA, Li Battery or USB power supply mode by configuring

| two pins | PWRM0 | and PWRM1. |

|----------|-------|------------|

|----------|-------|------------|

| PWRM1 | PWRM0 | PSU1(VDD) | PSU2(VCC) | PSU3(VDD) | Mode Descriptions                       |

|-------|-------|-----------|-----------|-----------|-----------------------------------------|

| 0     | 0     | On        | On        | Off       | 1x AA/AAA with more efficiency          |

| 0     | 1     | Off       | On        | On        | 1x AA/AAA with less external components |

| 1     | 0     | Off       | On        | On        | Two batteries                           |

| 1     | 1     | Off       | Off       | On        | USB power or Li battery                 |

The pin "PWRMode1" and "PWRMode0" have been pull down by on-chip resistor.

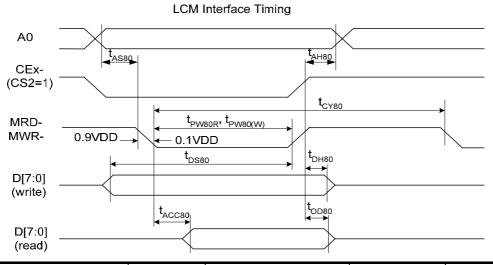

### 4.8 LCD Interface

ATJ2091H supports high-speed 8-bit parallel bi-directional LCM with 8080-series interface. LCM with 8080-series interface:

- Use GPIO to select data register or command register in LCM.

- > CE3- is used as chip select. Pin CS2 of LCM is pulled high to VCC.

- > MWR- is write enable signal. ATJ2091H latches D [7:0] at the rising edge.

- MRD- is read enable signal and LCM drives D [7:0] when MRD- is low.

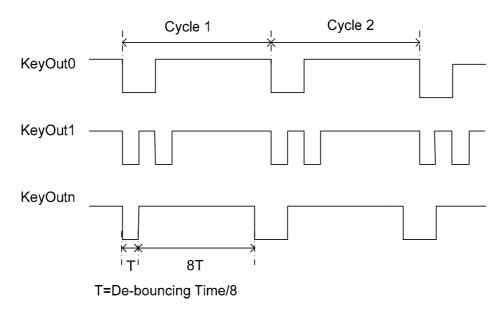

### 4.9 Key Scan Interface

**Key Scan Timing**

When key scan circuit is enabled, ATJ2091H will scan the keyboard periodically. It drives pin KEYOUTn [n=2...7] scan pulse in turn. When any key is pressed, the corresponding Keyout N will send out the scan pulse. When a key is pressed, pin Keyin N connecting the key will be found low level.

There are 12 internal 8-bit registers for key value latch per scan. But only another one register (Key Scan Data Register) for MCU may access key value. Those 12 internal registers are mapped into this register, and an internal pointer is used to point to the current register to return scan data when read. Any IO write to this register will clear the internal register, and the pointer will increase by 1 and point to the next register after read is performed.

### 4.10 External Memory Interface

### 4.10.1 NAND Flash Interface

ATJ2091H can support NAND type flash from 64M to 4G bytes.

### 4.11 USB 2.0 SIE

### 4.11.1General Description

The Actions USB2.0 device controller is fully compliant with the Universal Serial Bus 2.0 specification. In high-speed mode this device is capable of transmitting or receiving data up to 480Mbps. This high performance USB2.0 device controller integrates USB transceiver, SIE, and provides multifarious interfaces for generic MCU, RAM, ROM and DMA controller. So it is suitable for a variety of peripherals, such as: scanners, printers, mass storage devices, and digital cameras. It is designed to be a cost-effective USB total solution.

### 4.11.2 Features

- Fully compliant with USB specification 2.0

- > Supports USB high speed (480Mb/s) and full speed (12Mb/s)

- > Supports control, bulk, Isochronous and Interrupt transfers

- ➤ Embedded USB high-speed transceiver which complies with Inter UTMI

- Supports DMA interface (16-bit)

- > 2K bytes configurable FIFO for endpoints and provides double buffer to increase throughput.

- Supports USB remote wake-up feature

- > Software controlled connection to USB bus for re-enumeration

#### 4.11.3 Flash Interface

The Flash Interface circuit is a programmable high performance HW State Machine which supports a lot features in the following text.

- Command and address control state machine

- Reading and writing timing generator

- ECC accelerator (Reed-Solomon & Hamming)

- Sense R/B# status

- Comply with "SmartMedia Software Algorithm Guidelines"

- Bad block detection and replacement

- MLC flash supported

## 4.11.4 USB Using Memory

# 5. Electrical Characteristics

### **5.1 Absolute Maximum Ratings**

| Parameter           | Symbol           | Typical | Rating       | Unit |

|---------------------|------------------|---------|--------------|------|

| 0 1 1               | VDD              | 2.0     | <u>+</u> 10% | V    |

| Supply voltage      | VCC              | 3.3     | <u>+</u> 10% | V    |

|                     | V <sub>IH</sub>  | 2.4     | <u>+</u> 10% | V    |

| Input voltage       | VIL              | 1.0     | <u>+</u> 10% | V    |

| Storage temperature | T <sub>stg</sub> |         | -65~150      |      |

#### Note:

- 1.  $T_0 = 25$  (Operating Temperature)

- 2. Do not short-circuit two or more output pins simultaneously.

- 3. If even one of the above parameters exceeds the absolute maximum ratings even momentarily, the quality of the product may be degraded. The absolute maximum ratings, therefore, specify the value exceeding which the product may be physically damaged. Use the product well within these ratings.

- 4. The specifications and conditions shown in DC Characteristics and AC characteristics are the ranges for normal operation and quality assurance of the product.

### 5.2 Capacitance

| Parameter         | Symbol          | Condition                       | MIN. | MAX. | Unit |

|-------------------|-----------------|---------------------------------|------|------|------|

| Input capacitance | Cı              | f <sub>C</sub> = 1 MHz          |      | 15   | pF   |

| I/O capacitance   | C <sub>IO</sub> | Unmeasured pins returned to 0 V |      | 15   | pF   |

Note:  $T_O = 25$  , VCC = 0 V.

### **5.3 DC Characteristics**

| Parameter                 | Symbol              | Condition                  | MIN.   | TYP. | MAX.        | Unit |

|---------------------------|---------------------|----------------------------|--------|------|-------------|------|

| High-level output voltage | V <sub>OH</sub>     | I <sub>OH</sub> = -2 mA    | 2.4    |      |             | V    |

| Low-level output voltage  | V <sub>OL</sub>     | I <sub>OL</sub> = 2 mA     |        |      | 0.4         | ٧    |

| High-level input voltage  | V <sub>IH</sub>     |                            | 0.6VCC |      | VCC+0.6     | V    |

| Low-level input voltage   | V <sub>IL</sub>     |                            | -0.3   |      | 0.4VCC      | ٧    |

| Input leakage current     | I <sub>LI</sub>     | VCC = 3.6 V, VI = VCC, 0 V |        |      | <u>+</u> 10 | uA   |

| Output leakage current    | I <sub>LO</sub>     | VCC = 3.6 V, VI = VCC, 0 V |        |      | <u>+</u> 5  | uA   |

|                           | I <sub>drive1</sub> | GPOA0,GPOA1,GPOA2          |        | 4    |             | mA   |

| GPIO                      |                     | GPIO_B2, GPIO_B4,          |        | 40   |             | A    |

| Drive                     | I <sub>drive2</sub> | GPIO_B5                    |        | 10   |             | mA   |

|                           | I <sub>drive3</sub> | Other GPIO                 |        | 2    |             | mA   |

|                           |                     | In Full speed mode (MCU    |        |      |             |      |

|                           |                     | run 24MHz in internal      |        | 21   | 25          | mA   |

|                           | I <sub>VDD</sub>    | SRAM, DSP run 36MIPS)      |        |      |             |      |

| Supply Current            |                     | In Standby mode            |        | 50   | 70          | uA   |

| (One battery mode)        |                     | In Full speed mode (MCU    |        |      |             |      |

|                           |                     | run 24MHz in internal      |        | 1.28 | 1.5         | mA   |

|                           | I <sub>VCC</sub>    | SRAM, DSP run 36MIPS)      |        |      |             |      |

|                           |                     | In Standby mode            |        | 18   | 40          | uA   |

### NOTES:

- 1.  $T_o$  = -10 to +70 , VDD = 2.0 V, VCC = 3.3 V

- 2.  $I_{VDD}$  is a total power supply current for the 2.5 V power supply.  $I_{VDD}$  is applied to the LOGIC and PLL and OSC block.

- 3.  $I_{VCC}$  is a total power supply current for the 3.3 V power supply.  $I_{VCC}$  is applied to the USB, IO, TP, and AD block.

### **5.4 AC Characteristics**

$$T_o = -10 \text{ to } +70$$

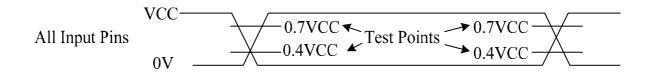

## 5.4.1 AC Test Input Waveform

## **5.4.2 AC Test Output Measuring Points**

All Output Pins

$$0.5$$

VCC  $\longleftarrow$  Test Points  $\longrightarrow 0.5$ VCC

### 5.4.3 Reset Parameter

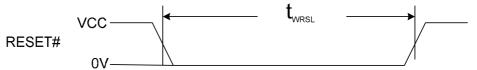

| Parameter                   | Symbol            | Condition  | MIN. | MAX. | Unit |

|-----------------------------|-------------------|------------|------|------|------|

| Reset input low-level width | t <sub>WRSL</sub> | RESET# pin | 160  |      | us   |

|                             |                   | 1          |      |      |      |

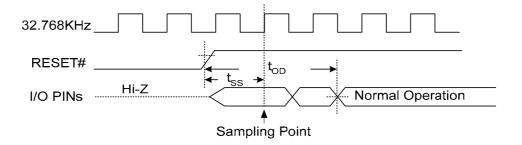

### 5.4.4 Initialization Parameter

| Parameter                       | Symbol          | Condition | MIN.  | MAX.  | Unit |

|---------------------------------|-----------------|-----------|-------|-------|------|

| Data sampling time              |                 |           |       | 04.04 |      |

| (from RESET# )                  | t <sub>SS</sub> |           |       | 61.04 | us   |

| Output delay time (from RESET#) | t <sub>OD</sub> |           | 61.04 |       | us   |

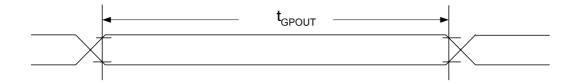

### **5.4.5 GPIO Interface Parameter**

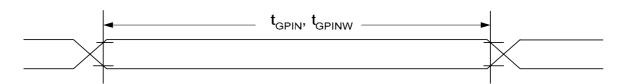

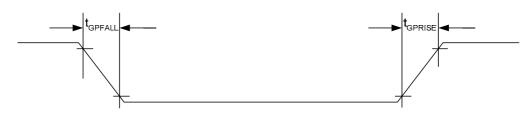

| Parameter            | Symbol              | Condition        | MIN.                    | MAX. | Unit |

|----------------------|---------------------|------------------|-------------------------|------|------|

| Input level width    | $t_{GPIN}$          |                  | 11/f <sub>mcuclk</sub>  |      | S    |

| GPIO input rise time | t <sub>GPRISE</sub> |                  |                         | 200  | ns   |

| GPIO input fall time | t <sub>GPFALL</sub> | Normal operation |                         | 200  | ns   |

| Output level width   | t <sub>GPOUT</sub>  |                  | 11/ f <sub>mcuclk</sub> |      | S    |

**Note:** 1. f<sub>MCUCLK</sub> is the frequency upon which MCU is running.

### **Input Level Width**

# **Input Rise/Fall Time**

### **Output Level Width**

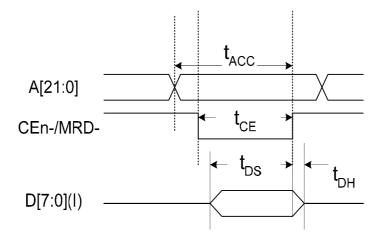

# **5.4.6 Ordinary ROM Parameter**

| Parameter                                    | Symbol           | Condition  | MIN. | MAX. | Unit |

|----------------------------------------------|------------------|------------|------|------|------|

| Data access time (from address) Note         | t <sub>ACC</sub> | HOSC=24MHz | 102  |      | ns   |

| Data access time (from CEx#) <sup>Note</sup> | t <sub>CE</sub>  | HOSC=24MHz | 82   |      | ns   |

| Data input setup time                        | t <sub>DS</sub>  | HOSC=24MHz | 0    |      | ns   |

| Data input hold time                         | t <sub>DH</sub>  | HOSC=24MHz | 0    |      | ns   |

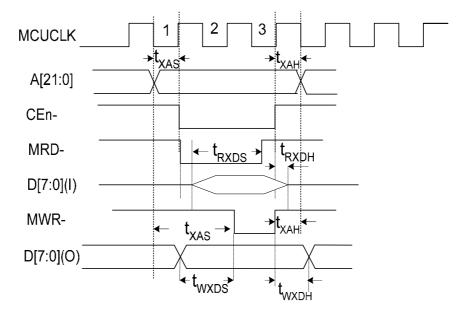

## 5.4.7 External System Bus Parameter

| Parameter                                                    | Symbol            | Condition    | Min. | Max. | Unit |

|--------------------------------------------------------------|-------------------|--------------|------|------|------|

| Address setup time (to command signal) <sup>Note 1, 2</sup>  | t <sub>XAS</sub>  | Memory Read  | 25   |      | ns   |

| Address setup time (to command signal)                       | t <sub>XAS</sub>  | Memory Write | 10   |      | ns   |

| Address hold time (from command signal) <sup>Note 1, 2</sup> | t <sub>XAH</sub>  |              | 5    |      | ns   |

| Data output setup time (to command signal) <sup>Note 1</sup> | t <sub>WXDS</sub> |              | 20   |      | ns   |

| Data output hold time(from command signal) <sup>Note 1</sup> | t <sub>WXDH</sub> |              | 10   |      | ns   |

| Data input setup time (to command signal) <sup>Note 1</sup>  | t <sub>RXDS</sub> |              | 20   |      | ns   |

| Data input hold time (from command signal) Note 1            | t <sub>RXDH</sub> |              | 10   |      | ns   |

Notes: 1. MRD#, MWR# are called the command signals for the External System Bus Interface.

2. T (ns) =

$$1/f_{MCUCLK}$$

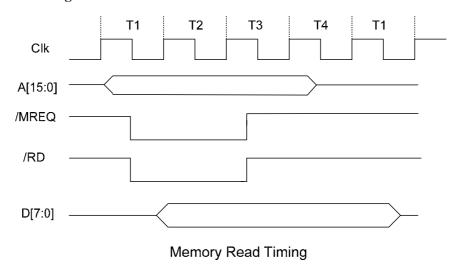

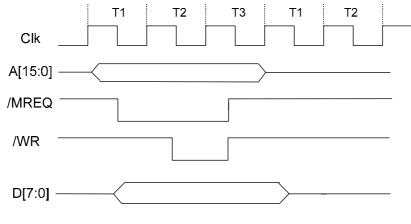

### 5.4.8 Bus Operation

### **Memory Read Timing**

### **Memory Write Timing**

Memory Write Timing

### 5.4.9 A/D Converter Characteristics

(TA = -10 - +70), VDD = 2.0 V, VCC = 3.3V, Sample Rate=32KHz)

| Characteristics                    | Min. | Тур. | Max.        | Unit |

|------------------------------------|------|------|-------------|------|

| Dynamic range                      |      | 78   |             | dB   |

| Total Harmonic Distortion + Noise  |      | 73   |             | dB   |

| Frequency Response (20-13KHz)      |      |      | <u>+</u> 5% | dB   |

| Full Scale Input Voltage(Gain=0dB) |      | 2    |             | m∨pp |

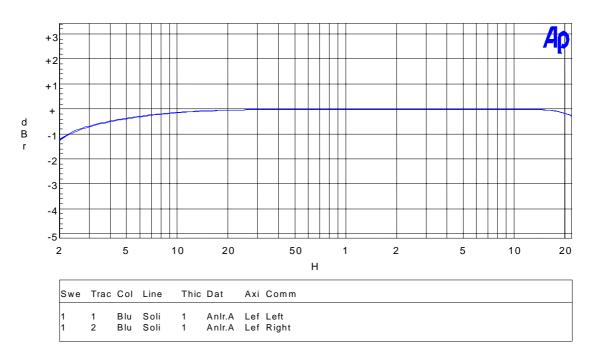

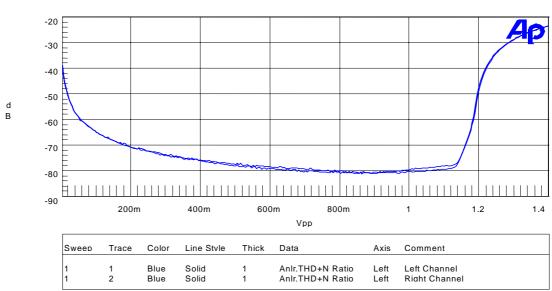

### **5.4.10 Headphone Driver Characteristics Table**

$(T_o$  =-10 - +70 , VDD = 2.0 V, VCC = 3.3 V, Sample Rate=32KHz, Volume Level=0x1F)

| Characteristics                   | Min. | Тур. | Max.       | Unit |

|-----------------------------------|------|------|------------|------|

| Dynamic Range -60 dBFS Input      |      | 86   |            | dB   |

| Total Harmonic Distortion + Noise |      | 80   |            | dB   |

| Frequency Response 20-20KHz       |      |      | <u>+</u> 1 | dB   |

| Output Common Mode Voltage        |      | 1.5  |            | V    |

| Full Scale Output Voltage         |      | 1.2  |            | Vpp  |

| Inter channel Gain Mismatch(1KHz) |      | 11   |            | dB   |

### Frequency Response Diagram of Headphone Driver

Audio ATJ2091 PA Frequency Response @1Vpp

THD + N Amplitude Diagram of Headphone Driver

Audio Precision ATJ2091 PA THD+N vs Amplitude

@ 1KHZ 16ohm\*220uF

### 5.4.11 LCM Driver Parameter

| Parameter               | Symbol               | Condition  | Туре | Unit |

|-------------------------|----------------------|------------|------|------|

| Data access time(write) | t <sub>PW80(W)</sub> | HOSC=24MHZ | 29   | ns   |

| Data access time (Read) | t <sub>PW80(R)</sub> | HOSC=24MHZ | 67   | ns   |

| Write cycle time        | t <sub>CY80(W)</sub> | HOSC=24MHZ | 407  | ns   |

| Read cycle time         | t <sub>CY80(R)</sub> | HOSC=24MHZ | 284  | ns   |

| Data setup time         | t <sub>DS80</sub>    | HOSC=24MHZ | 79   | ns   |

| Data hold time          | t <sub>DH80</sub>    | HOSC=24MHZ | 8    | ns   |

| Address setup time      | t <sub>AS80</sub>    | HOSC=24MHZ | 11   | ns   |

| Address hold time       | t <sub>AH80</sub>    | HOSC=24MHZ | 11   | ns   |

| Read access time        | t <sub>ACC80</sub>   | HOSC=24MHZ | 13   | ns   |

| Data input hold time    | t <sub>OD80</sub>    | HOSC=24MHZ | 8    | ns   |

# 6. Ordering Information

### 6.1 Soldering Conditions

| Soldering Process      | Soldering Conditions                                                  |

|------------------------|-----------------------------------------------------------------------|

|                        | Peak package's surface temperature: 235°C(Lead) or 260°C(Lead Free)   |

|                        | Reflow time: 30 seconds or less (210°C or more)(Lead) or              |

| Infrared roy refley    | 60 seconds or less (217°C or more) (Lead Free)                        |

| Infrared ray reflow    | Maximum allowable number of reflow processes: 2                       |

|                        | Exposure limit: 1 days at Rh=60%,Tem=30 °C (12 hours of pre-baking is |

|                        | required at 125°C afterward).                                         |

| Dartial hasting mathed | Terminal temperature: 300°C or less                                   |

| Partial heating method | Heat time: 3 seconds or less (for one side of a device)               |

#### Note:

Maximum number of days during which the product can be stored at a temperature of 25℃ and a relative humidity of 65% or less after dry-pack package is opened.

#### Caution:

Do not apply two or more different soldering methods to one chip (except for partial heating method for terminal sections).

### 6.2 Precaution Against ESD For Semiconductors

Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work

# ATJ2091H PRODUCT DATASHEET

bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

### 6.3 Handling of Unused Input Pins For CMOS

No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS devices behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

### 6.4 Status Before Initialization of MOS Devices

Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on.

# 7. ATJ 2091H Package Drawing

| , , ,                                         | NOM. MAX.   | - 0.063                                    | 0.006                                                        | 0.055 0.057  | BASIC                                  | BASIC       | BASIC       | BASIC         | 0.008    | 1            | 5. 7.        |          | 13.            | 13*     | - 0.008  | 0.004 0.005 0.006 | 0.039 REF | 0.018 0.024 0.030                     |       | 0.011         | 0.008 0.009 0.009 | 0.020 BSC. | 0.008 | 0,008 | 0.003 | 0.003 |

|-----------------------------------------------|-------------|--------------------------------------------|--------------------------------------------------------------|--------------|----------------------------------------|-------------|-------------|---------------|----------|--------------|--------------|----------|----------------|---------|----------|-------------------|-----------|---------------------------------------|-------|---------------|-------------------|------------|-------|-------|-------|-------|

| RS.                                           | MIN.        |                                            | 0.002                                                        | 0.053 0.0    | 0.472 BASIC                            | 0.394 BASIC | 0.472 BASIC | 0.394 BASIC   | 0.003    | 0.003        | 3.5          | 1        | . 12.          | . 12.   | 0.004    | 0.0 4 O.C         | 0.038     | 118 0.0                               | 0.008 | 0.007         | 107 0.0           | 0.020      | ŏ     | ö     | 0.0   | 0     |

| LLIMETE                                       | MAX.        | 1.60                                       | 0.15 0.0                                                     | 1.45 0.0     |                                        |             |             |               | 0.20 0.0 | 0.0          | 7 0.         | ъ<br>П   | 13. 11.        | 13* 11* | 0.20 0.0 | 0.16 0.0          |           | 0.75 0.0                              | 0.0   | 0.27 0.0      | 0.23 0.0          |            | +     |       |       |       |

| IS ARE IN MI                                  | NOM.        | <del>-</del>                               | о́<br>                                                       | 1.40 1.      | 12.00 BASIC                            | 10.00 BASIC | 12.00 BASIC | 10.00 BASIC   | о́<br>   | <u>'</u><br> | 3,5          |          | 12.            |         | о<br>П   | 0.127 0.          | 1.00 REF  | 0.60 0.                               | 1     |               | 0.20 0.           | 0,50 BSC.  | 0.20  | 0.20  | 0.08  | 0.07  |

| ONS AR                                        | M<br>N<br>N | <u>                                   </u> | 0.05                                                         | 1.35         | 12.00                                  | 10.00       | 12.00       | 10,00         | 0.08     | 0.08         |              |          | 11. 12         | 11' 12* | - 60.0   | 0.09 0.           | 1.00      | 0.45                                  | 0.20  | $\rightarrow$ | 0.17 0            | 3.0        |       |       |       |       |

| ALL DIMENSIONS ARE IN MILLIMETERS. MILLIMETER | SYMBOL      | <b>∀</b>                                   |                                                              | A2 1         | 0                                      | 01          | ш           | E 1           | R 2 0    | R1 0         | 0.           | ٠.<br>۵، | Q <sub>2</sub> | 93      | ٥        | 0 10              |           | 0 7                                   | s o   | T             | _                 | D)         | daa   | qqq   | 202   | ppp   |

| ALI                                           | <u> </u>    |                                            |                                                              |              |                                        |             |             |               |          |              |              |          |                |         |          |                   |           |                                       |       |               |                   |            |       |       |       |       |

| 49 IIIII                                      |             | <u>2</u><br>11441                          | 1910<br>1910<br>1910<br>1910<br>1910<br>1910<br>1910<br>1910 | <b>1</b> 144 | ************************************** |             |             | $\overline{}$ | 32.61    |              | 4X Ogg CA-BD |          |                |         |          |                   | -         | ◆   ddd(W) C   A-B D   SFATING PI ANF |       |               |                   |            |       | 74    |       |       |

Actions Semiconductor Co., Ltd.

Address: 15-1, NO.1, HIT Road, Tangjia, Zhuhai, Guangdong, China

Tel: +86-756-3392353

Fax: +86-756-3392251

**Post code: 519085**

${\bf http://\ www.actions\text{-}semi.com}$

$Business\ Email:\ mp\text{-sales} @\ actions\text{-semi.com}$

Technical Service Email: mp-cs@actions-semi.com